Process Design Kits (PDKs)

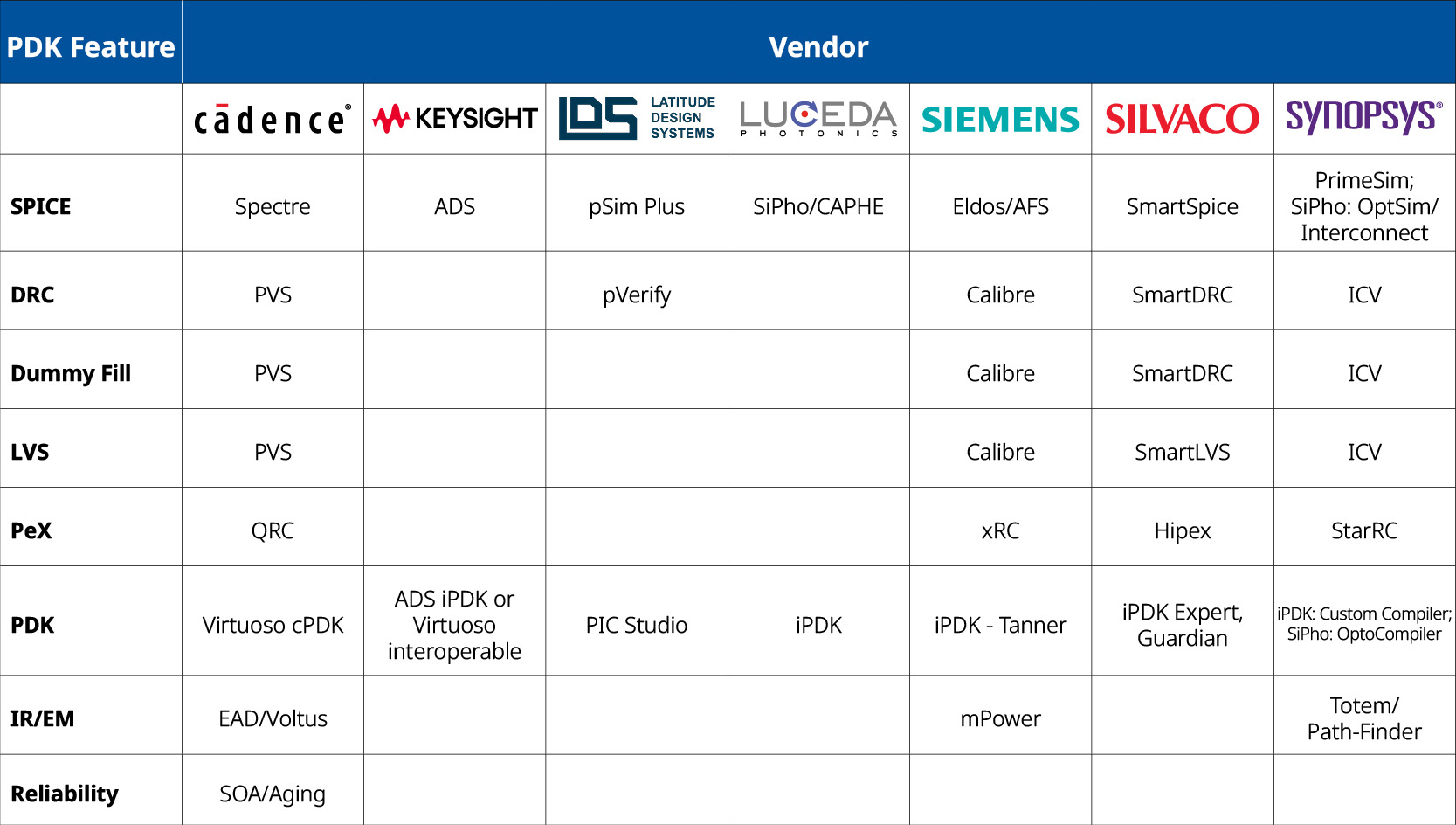

Tower Semiconductor PDKs offer a front-to-back integrated custom design environment that supports most major EDA vendors’ design flows.

Tower Semiconductor PDKs use sophisticated analytical techniques to warn designers when they have exceeded the electrical Safe Operating Area (SOA), allowing design optimization for reliability. In addition, silicon verified, highly scalable device models and robust physical design tools are available for up front design optimization. These powerful and efficient tools enable unprecedented accuracy in circuit simulation and Tower Semiconductor’s unparalleled customer support at every stage of the design flow ensures confidence in designs at near zero risk, reducing time to market.

Tower Semiconductor design enablement platform includes:

- Cadence® Virtuoso® PDKs with interoperability with Keysight ADS for select flows

- iPDKs for select processes to support Custom Compiler, ADS, and Tanner, EDA environments

- Scalable models with RF/analog accuracy such as PSP for MOSFETs, MOSVAR, HiCUM for BJTs, R3 for resistors, HiSIM_SOI for RF SOI and HiSIM_HV for LDMOS devices

- Scalable layout cells (p-cells), tightly coupled to the underlying models with features targeted for end applications enabling quick synthesis of layout blueprints

- Monte Carlo statistical and mismatch simulation capability

- PCM based models allowing design sensitivity analysis

- X-Sigma – a unique process variation modeling tool enabling tradeoff of yield vs. performance

- An industry-first scalable drift length LDMOS providing the highest level of SOA vs. performance

- Design tools such as Inductor and Balun toolbox and foundry certified EM decks tailored to the needs of RF design from cellular to 5G and higher

- Analog/RF friendly dummy fill and slotting solutions that help optimize the performance/yield trade-off

- Extensive layout utilities to speed up gds synthesis time

- Parasitic extraction and back-annotation integrated with model and layout features, including new capabilities for Flip-Chip packaging

- Silicon verified substrate modeling capabilities embedded within the PDK

- Advanced electrical checking for both devices and interconnects ensuring their reliability limits

- Self-consistent electro-thermal simulation enablement via Keysight ETH and Cadence Legato in select flows

- Reference Design Flows – silicon validated reference flows for power management and SOI switch designs highlighting proper use of PDK and models

- PERC reliability checks for analog and automotive design – ESD, RESCAR constraint check, voltage aware propagation & DRC and P2P

- Best-in-class design enablement for silicon photonics with support for Ansys INTERCONNECT, Cadence CurvyCore, GDS Factory, Latitude Design Systems, Luceda, Siemens Tanner, Klayout based DRC from Spark Photonics, and Synopsys OptoCompiler, with Verilog-A models for electro-optic simulations in SPICE simulators

Tower Semiconductor Supported PDK Flows